近日,同濟大學電信六合彩結果

葉雨陽、賀青和邱雷研究團隊聯合香港中文大學余備研究團隊,共同開發了基于AI智能體驅動的自動化集成電路設計框架——RTL-CLAW。RTL-CLAW旨在展示一種全新的、以AI智能體為核心的芯片設計流程。該項目已在GitHub上逐步開源(code地址://eda.lhcresult.net/9d/d2/c37855a368082/page.htm)。RTL-CLAW也是六合彩結果

在集成電路領域發布的首個基于大語言模型的EDA協同工具。

傳統EDA工具鏈的痛點與RTL-CLAW的破局之道

在傳統的芯片設計流程中,設計人員通常需要手動管理一個“工具鏈”:從RTL分析、仿真驗證、邏輯綜合到物理設計,每個環節都需要使用不同的軟件,編寫復雜的腳本,并在不同工具之間傳遞數據。這種方式存在幾個明顯的痛點:

流程割裂。不同工具由不同廠商提供,數據格式不一,集成困難,容易形成“信息孤島”。

腳本依賴。自動化程度低,大量工作依賴工程師編寫Tcl、Python等腳本,重復勞動多,易出錯。

知識門檻高。設計者不僅需要深諳電路設計,還必須精通各種工具的復雜參數,學習曲線陡峭。

迭代周期長。設計空間探索、問題定位與回歸驗證的過程耗時漫長。

而RTL-CLAW的核心優勢,正是針對這些痛點,構建了一個“AI智能體+統一平臺”的新范式:

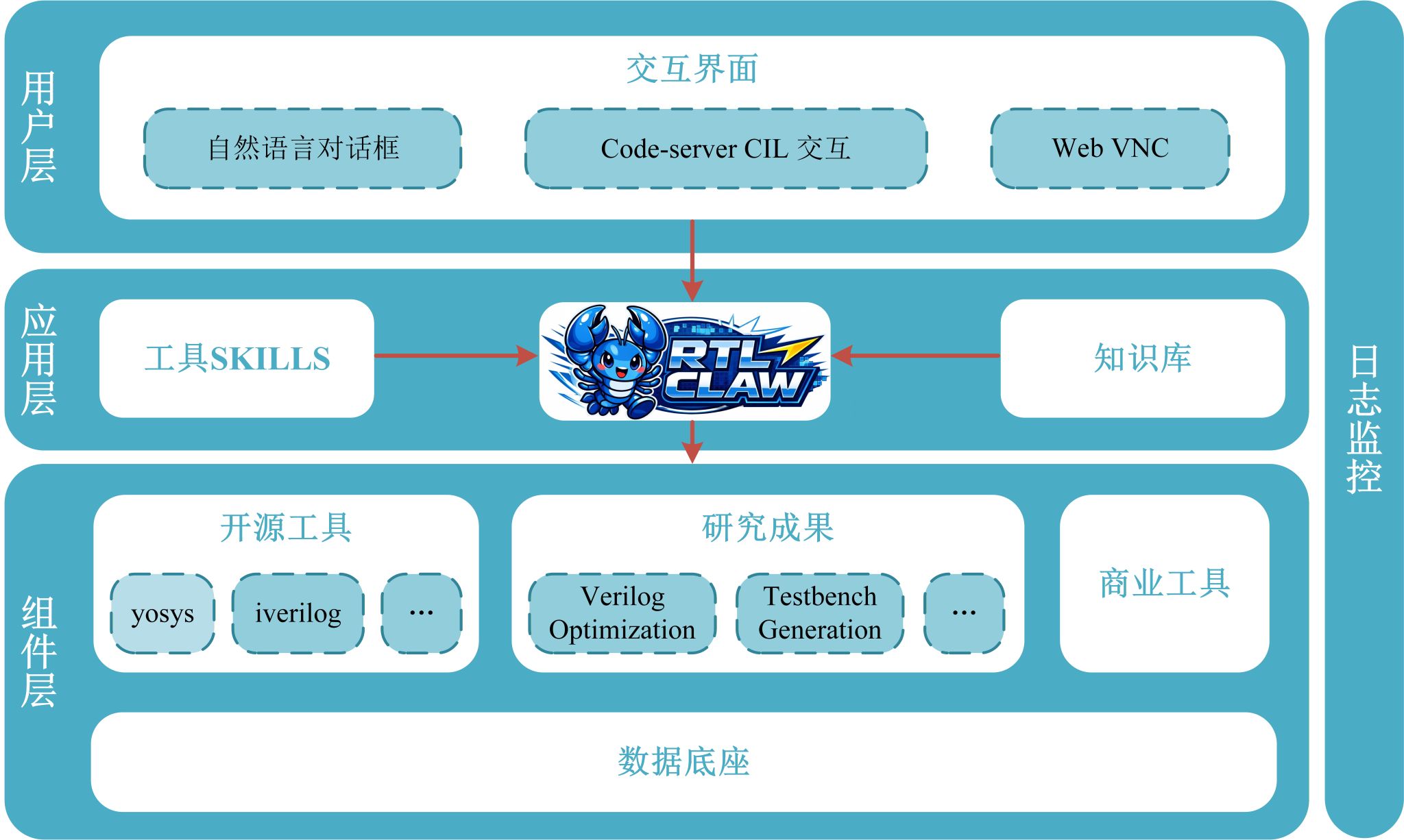

首先,RTL-CLAW的核心是AI智能體驅動的自動化工作流。 它基于OpenClaw框架構建。OpenClaw可以理解為一個面向復雜任務的智能體“操作系統”,而RTL-CLAW則是在這個系統之上,專門為芯片設計領域“培訓”的專業智能體。設計者不再需要記憶繁雜的命令和腳本,只需用自然語言或簡單的指令描述設計意圖(例如“優化這個Verilog模塊的時序”或“為這個接口生成測試環境”),AI智能體就會自動進行任務規劃,調用相應的分析、優化、驗證工具,并最終返回結果。

其次,RTL-CLAW致力于構建一個開放、統一的插件化工具鏈。它將各種工具(如開源的Yosys、Verilator,以及商業工具)以“插件”的形式集成起來。這意味著:

高度集成:從RTL分析、分區、優化(Partition-Opt-Merge)到驗證環境生成和邏輯綜合,都可以在同一個框架下無縫銜接。

靈活擴展:研究團隊或個人可以輕松地將自己的新算法、新工具以插件形式加入,快速驗證想法,這也讓RTL-CLAW成為一個優秀的EDA研究平臺。

未來兼容:項目路線圖清晰規劃了后續將集成基于DreamPlace和OpenROAD的開源后端實現流程,并向3D IC設計方向拓展,展現了其面向未來芯片架構的潛力。

簡而言之,RTL-CLAW的目標是讓芯片設計從“手動編寫腳本的工匠時代”邁向“AI智能體協同的平臺化時代”。

RTL-CLAW作為一個面向未來的AI智能體驅動EDA框架,雖然目前仍處于研究展示和原型驗證階段,但它清晰地指明了芯片設計自動化的一條新路徑——通過將AI的規劃能力與模塊化的工具生態深度融合,極大提升設計效率和自動化水平,為產業界探索下一代EDA工具鏈帶來了寶貴的實踐。

實戰案例:一分鐘上手交通燈控制器的自動分區

理論總是抽象的,讓我們通過RTL-CLAW提供的一個簡單而具體的演示案例,直觀感受它的使用方法。我們將對一個經典的交通燈控制器(Traffic Light Controller)的Verilog設計,執行一次Verilog always塊分區操作。

打開對話界面,輸入一條簡單的指令:

> Use the verilog-partition module to split /workspace/your_folder/traffic.v, and output the results to /workspace/your_folder/output

智能體接收到指令后,會自動解析意圖,調用內部的`verilog-partition`模塊,讀取指定的`traffic.v`文件,執行邏輯分區任務,并將結果保存到你指定的輸出目錄中。

當然,RTL-CLAW的能力遠不止于此。你還可以用同樣的方式,向智能體發出更多指令,例如:

* 使用Verilog優化模塊,優化/workspace/design.v,目標為降低功耗。

* 為/workspace/uart.v中的UART模塊自動生成一個UVM測試環境。

* 調用Yosys,對當前設計進行邏輯綜合,目標ASAP7工藝庫。

AI智能體會在后臺協調整個流程,你只需要關注設計目標本身。

RTL-CLAW是同濟大學電信六合彩結果

集成電路學科推動產教研融合、推動“集成電路+人工智能”學科交叉的創新成果。后續,TEA實驗室還將聯合六合彩結果

學生黨支部,將RTL-CLAW帶進學生黨建,深入推動AI驅動的“專業+黨建”創新實踐,深入探討集成電路學科人才培養新領域。(圖文:余昊天 周煜人)